Pazartesi günü Intel, Intel 18A ve 20A (18/20 angstroms, 1.8/2.0nm sınıfı) fabrikasyon süreçlerinin bir parçası olacak bir arka taraf güç dağıtım ağı (BS PDN) uygulamasının ayrıntılarını verdi. Ayrıca şirket, bu teknolojinin en iyi BS PDN için özel olarak tasarlanmış dahili Intel 4 + PowerVia düğümü için sağladığı avantajlar hakkında daha fazla bilgi de açıkladı.

Arka Taraf Güç Dağıtımı

Intel’in 18A ve 20A üretim teknolojileri, iki önemli yeniliği ortaya çıkaracak: ŞeritFET kapısı çepeçevre alan etkili transistörler (GAAFET’ler) ve PowerVia arka taraf güç dağıtım ağı. GAA transistörlerinin avantajları daha önce tartışılmıştır ve bugünün duyurusunun kapsamı dışındadır. Bunun yerine arka taraf güç dağıtımına odaklanacağız.

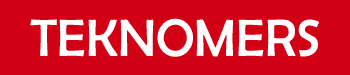

Arka taraftaki güç rayı, güç hatlarını levhanın arkasına kaydırarak güç ve G/Ç kablolarını ayırmayı amaçlar. Bu yöntem, hat arkası ucundaki (BEOL) direncin artması gibi sorunları çözer, sonuç olarak transistörlerin performansını iyileştirir ve güç tüketimini düşürür. Ayrıca veri ve güç kabloları arasındaki olası parazitleri ortadan kaldırır ve lojik transistör yoğunluğunu artırır.

Zamanla, BD PDN standart bir çip özelliği haline gelecek, ancak şimdilik Intel, 2003’te 90nm’de gerilmiş silikona, 2007’de 45nm’de Hafnium tabanlı yüksek K metal geçidine ve 2012’de 22nm’de FinFET’e benzer büyük bir çığır açan yenilik olarak görüyor. .

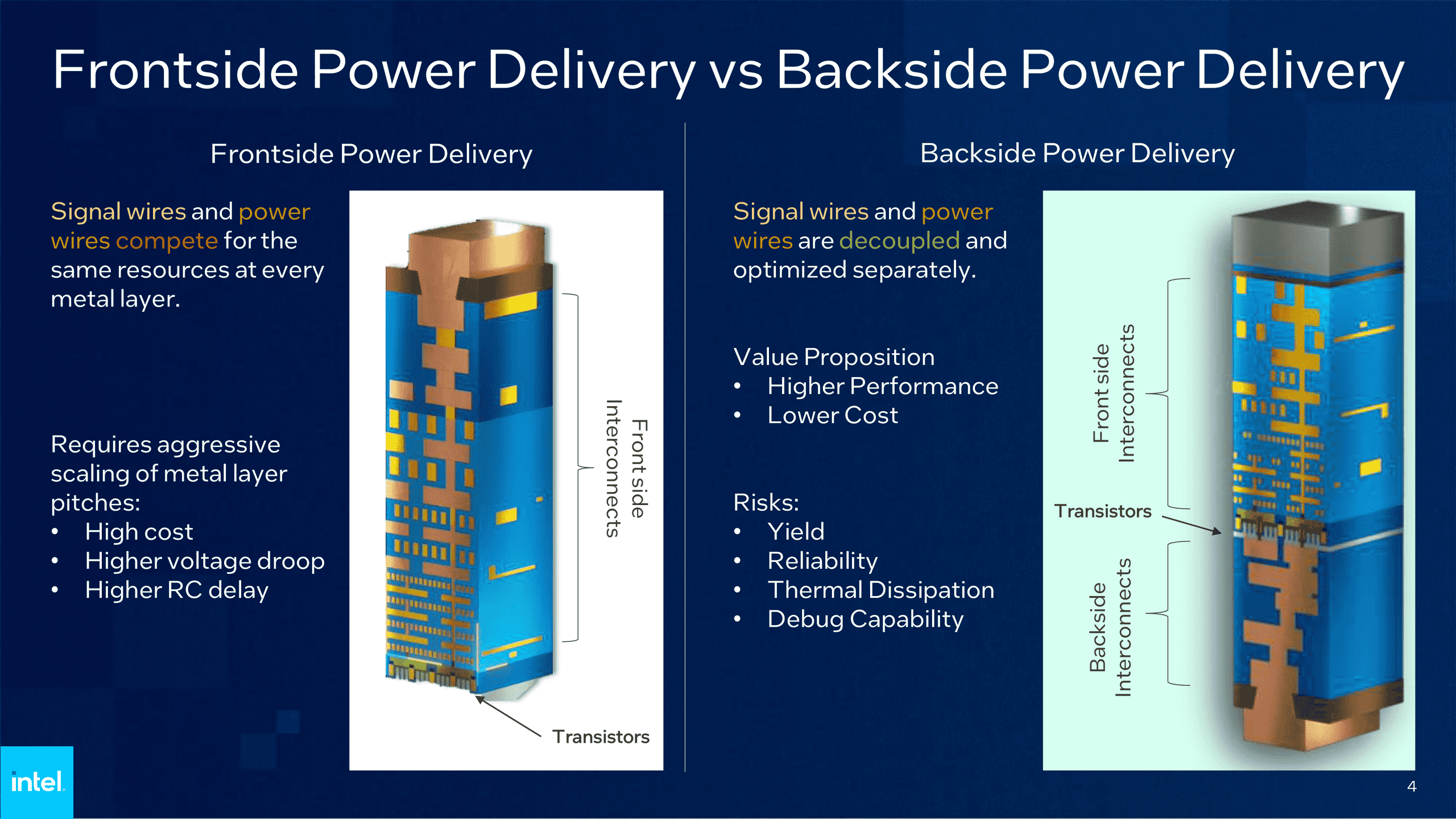

Intel, dahili bir işlem düğümündeki bir test çipinde uygulandığında, arka taraf PDN’sinin saat hızını %6’nın üzerinde artırmasını, IR voltaj düşüşünü %30 azaltmasını ve E-çekirdek kalıbının geniş alanlarında hücre kullanımını artırmasını sağladığını söylüyor. %90’ın üzerinde. Avantajlarına rağmen, bir arka taraf güç dağıtımını uygulamak ve inşa etmek birkaç nedenden dolayı zorludur.

PowerVia Arka Taraf PDN’si Oluşturma

Bir arka taraf PDN oluşturmak, geleneksel ön taraf güç dağıtımından çok farklıdır. En gelişmiş çiplerin bile üretimi bugünlerde oldukça basit. Her yonga levhanın üretimi, EUV tarayıcılar gibi en gelişmiş üretim araçlarını kullanarak 30nm kadar küçük (Intel 4 düğümü için) en karmaşık M0 transistör katmanından başlar. Daha sonra yonga üreticileri, ilkinin üzerine daha az karmaşık transistör katmanları inşa eder ve tüm katmanları birbirine bağlamaları ve tüm transistörlere güç vermeleri gerektiğinden boyutları kademeli olarak artırır.

G/Ç ve güç için gerçek fiziksel kablolar, transistör katmanlarıyla karşılaştırıldığında devasa görünüyor ve her yeni nesilde bunları düzgün bir şekilde yönlendirmek daha zor ve daha pahalı hale geliyor.

Intel’in PowerVia BS PDN’sine sahip yongalarla bir gofreti işlemek, tüm karmaşık mantık katmanlarının yanı sıra sinyal kablolarını üretmeyi, ardından gofreti ters çevirmeyi ve mantığın “üstüne” güç dağıtım ağını oluşturmayı içerir. Kağıt üzerinde, böyle bir ‘takma’ büyük bir anlaşma gibi görünmüyor. Bununla birlikte, mantık transistörlerinin üzerine PDN oluşturmak için gofretten ‘fazla’ silikonun çıkarılması, CMP temizliği, metroloji, litografi ve dağlama gibi oldukça fazla işlem adımı ekler.

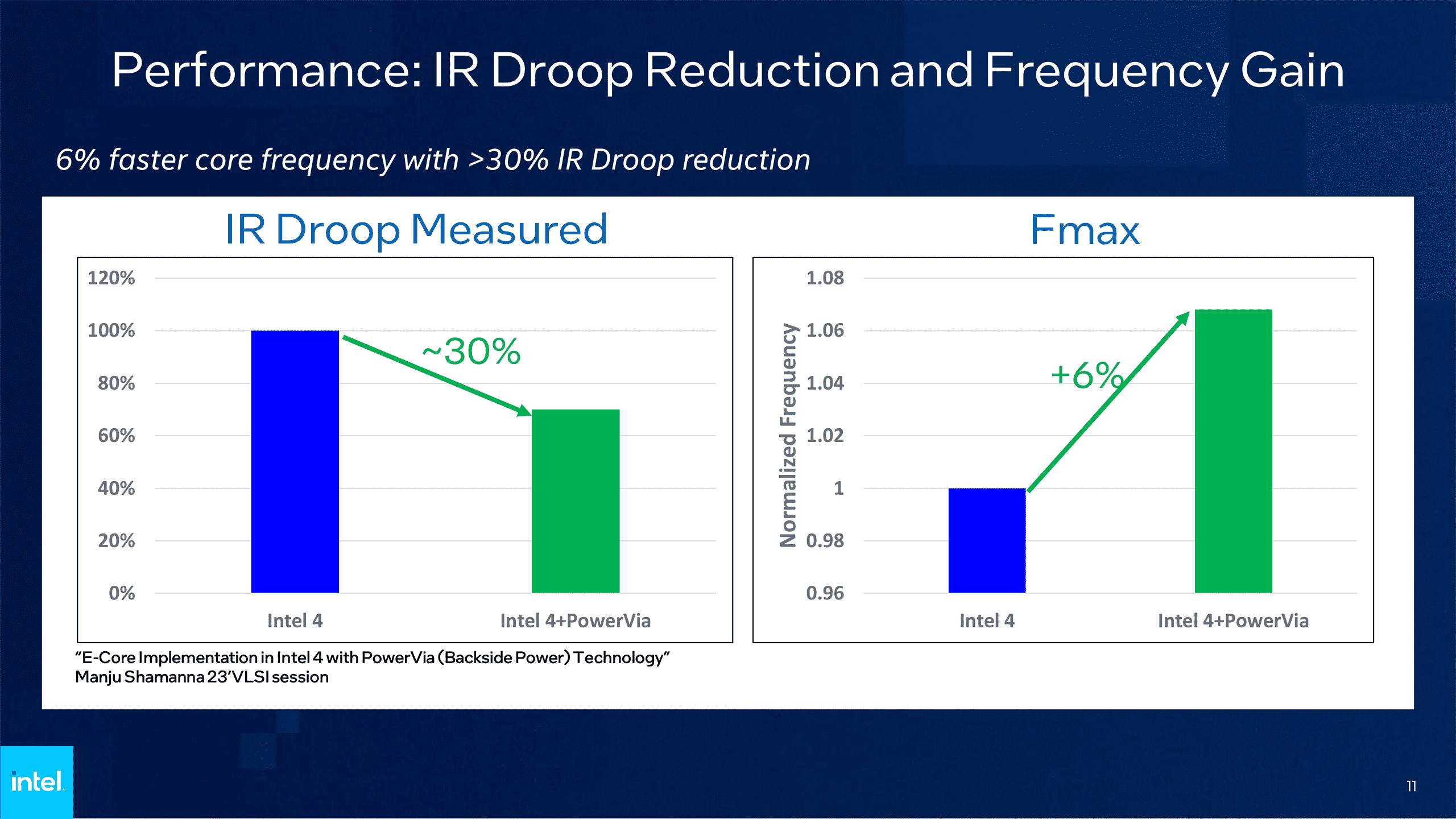

Böyle bir süreç döngüsü, fabrikadaki en gelişmiş araçları gerektirmeyebilir, ancak yine de maliyetlidir. Aslında bir Intel slaytı, Intel 4 işlem teknolojisinin 15 metalik katman ve bir yeniden dağıtım katmanı (RDL) kullandığını gösterirken, Intel 4 + PowerVia’nın 14 ön yan katman, dört arka yan katman ve toplam katman sayısını artıran bir RDL kullandığını gösterir. 18 + RDL’ye.

Intel’de Teknoloji Geliştirme Başkan Yardımcısı Ben Sell, “Daha önce olduğu gibi önce transistörler yapılıyor, sonra ara bağlantı katmanları ekleniyor” dedi. “Şimdi eğlenceli kısım: gofretin tersini çevirin ve tellerin bağlandığı alt katmanı ortaya çıkarmak için her şeyi parlatın. […] için güç bağlanacaktır. Biz buna silikon teknolojisi diyoruz ama bu gofretlerde kalan silikon miktarı gerçekten çok az.”

Bir arka taraf PDN’si ile dikkate alınması gereken birkaç faktör vardır. İlk olarak, üretim sürecini büyük ölçüde değiştirdiği için Intel, radikal değişikliklere rağmen yüksek verim sağlamanın bir yolunu bulmak zorunda kaldı. İkinci olarak Intel, arka taraftaki PDN’nin mevcut PDN’si kadar güvenilir olmasını ve amaçlandığı gibi çalışmasını sağlamalıydı. Üçüncüsü, G/Ç ve güç kabloları artık transistörlerin her iki yanında yer aldığından, çipleri soğutmak ileride daha da zorlaşacaktır. Dördüncüsü, Intel’in transistör katmanlarına erişmek için arka taraftaki güç ara bağlantılarını kaldırması gerektiğinden, çiplerde hata ayıklamak önemli ölçüde zorlaşıyor.

Intel’in PowerVia işlemiyle ilgili başka bir özellik daha var. Intel, gofretin arkasındaki fazla silikonu çıkardığı için sertliğini kaybettiğine inanıyor, bu yüzden yapıyı bir arada tutmak için gofretin sinyal tarafına bir taşıyıcı gofreti yapıştırıyor. Bu taşıyıcı gofret de sonunda incelir, ancak eklenmesi de karmaşık (ve muhtemelen gerekli) bir işlem adımıdır.

Intel’in PowerVia arka PDN’si ile ilgili başka bir şey de, BS PDN ile gömülü güç raylarını kullanmaması, bunun yerine gücü doğrudan transistör katmanına iletmek için silikon yoluyla nano ölçekli geçişlere (TSV’ler) güvenecek olmasıdır. Şirketin teknolojisine PowerVia adını vermesinin nedeni bu.

Arka Taraf Güç Dağıtım Ağını Test Etme

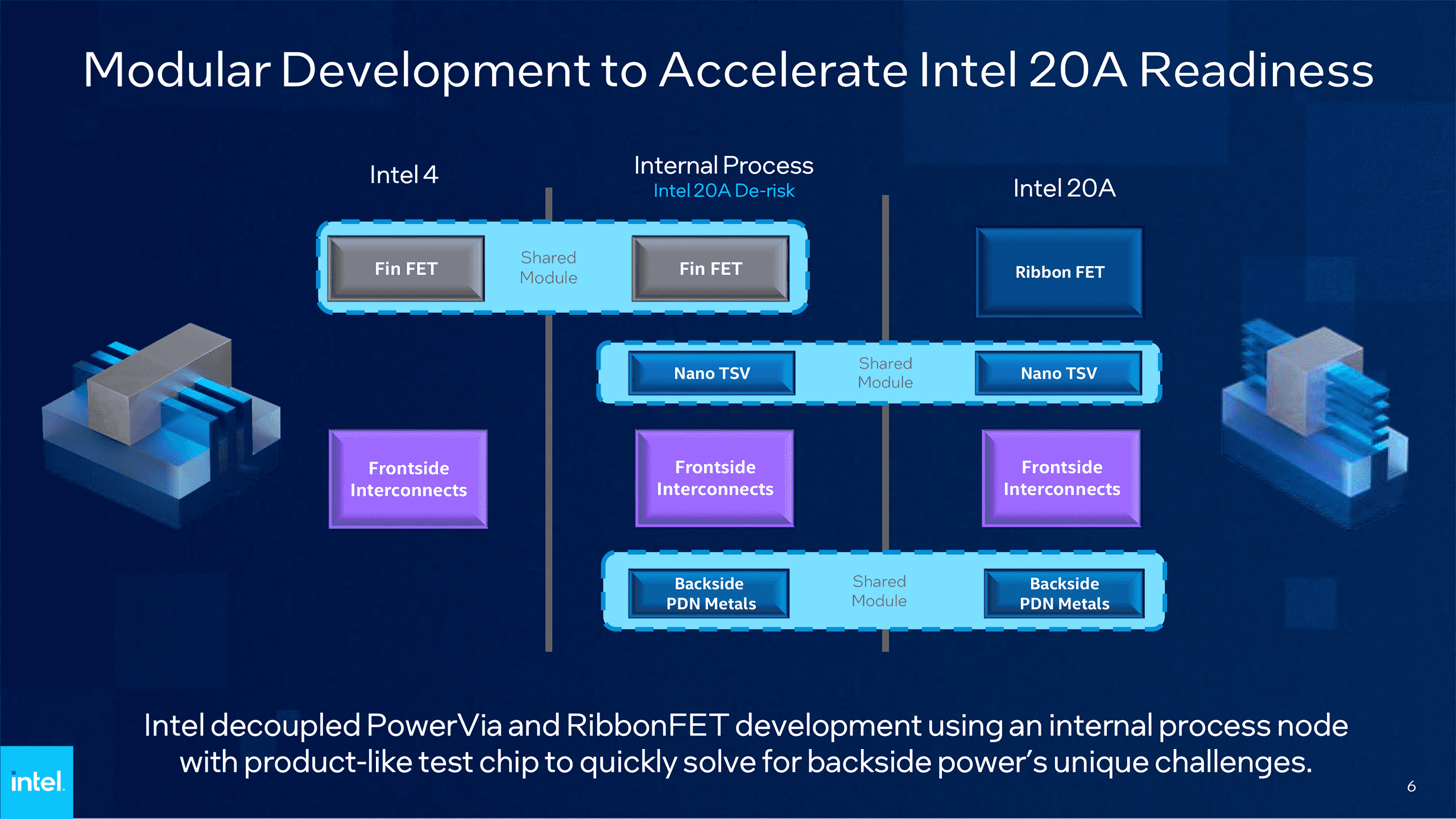

Artık Intel, en iyi işlem teknolojilerine sahip çip pazarının tartışmasız lideri olmadığına göre, şirket yeni nesil düğümlerinden birinde olası bir arıza noktasını riske atamaz. Bu nedenle, normal bir PDN ile RibbonFET’ler üzerinde çalışarak ve ardından kanıtlanmış FinFET’lerle PowerVia’da hata ayıklayarak geliştirme sürecini biraz daha kolaylaştırmak için RibbonFET GAA transistörlerinin ve PowerVia BS PDN’nin geliştirilmesini ayırdı.

Intel, PowerVia arka güç dağıtım ağını test etmek için kanıtlanmış FinFET transistörleri kullanan Intel 4 düğümüne dayalı özel bir üretim süreci oluşturdu, ancak geleneksel bir güç rayı yerine bir arka taraf güç rayıyla birlikte geliyor. Bu işlem doğal olarak Intel 4 + PowerVia olarak adlandırılır ve Blue Sky Creek kod adlı bir test çipi için kullanılır.

Intel’in Blue Sky Creek test çipi, her biri Crestmont mikro mimarisine dayanan enerji açısından verimli dört çekirdeğe sahip iki kalıp kullanır. Bunlar 1,1 Voltta 3 GHz’de çalışacak şekilde tasarlanmıştır. Test aracı yalnızca iki amaç için tasarlanmıştır: PowerVia BS PDN’nin avantajlarını keşfetmek ve PDN’nin verimleri, güvenilirliği dahil olmak üzere yeni güç dağıtım ağıyla ilgili her şeyi test ederek gelecekteki 20A/18A işlem teknolojilerinden kaynaklanan riski ortadan kaldırmak ve çip, soğutma ve hata ayıklama.

Verim söz konusu olduğunda Intel, Intel 4 ve Intel 4 + PowerVia’da uygulanan test çipinin kusur yoğunluğunun neredeyse aynı olduğunu söylüyor. Güvenilirlik ve transistör özellikleri hedefleri de üretim için gerekli beklentileri karşıladı. Ayrıca test aracının ısıl değerleri de beklentilere uygun çıktı. Bu arada Intel, arka taraf PDN ile soğutmanın zor olacağını kabul ediyor, bu nedenle yeni nesil yongaları soğutmak için yeni termal hafifletme şemaları geliştirdi.

Sell, “Normalde ısı dağılımı için silikon tarafı da kullanırsınız,” diye açıkladı. “Artık transistörlerinizi sıkıştırdınız ve soru şu: ‘Isıl bir sorunumuz mu var? Çok fazla yerel ısınma alıyor muyuz?’ Bu noktada muhtemelen cevabı tahmin edebilirsiniz: hayır.”

Hata ayıklama muhtemelen en karmaşık kısımlardan biriydi, ancak şans eseri Intel’in doğrulama mühendisleri zorlukların üstesinden gelmenin bir yolunu buldular.

Sell, “Pek çok endişe ve tereddüt vardı ve bu muhtemelen anlaşılması en zor şeydi – bu yeni arka taraf güç dağıtımında hata ayıklamanın nasıl yapılacağı” dedi. “İşleri daha da zorlaştırmak için, test çipi tasarım ekibi, doğrulama ekibinin haberi olmadan kasıtlı olarak çipe bazı ‘easter egg’ hataları ekledi. İyi haber mi? Hataları buldular. Son birkaç yılda muazzam ilerleme kaydettik. Bu hata ayıklama yeteneklerini geliştirmede ve bunları Blue Sky Creek’te kanıtlamada yıllar geçti.”

Intel’in PowerVia BS PDN’si 2024’te Geliyor

Intel’in PowerVia arka güç dağıtım ağını kullanan halka açık ilk işlem teknolojileri, sırasıyla 2H 2023 ve 1H 2024’te üretime hazır olacak 20A ve 18A düğümleri olacaktır. Intel’in 20A fabrikasyon sürecinde üretilecek ilk istemci CPU’su, 2024 ortalarında veya daha önce piyasaya sürülmesi beklenen Arrow Lake’dir.

Intel’in 18A ve 20A üretim teknolojileri, hem şirketin kendi ürünleri hem de Intel Döküm Hizmetleri müşterileri için geliştirildiğinden, PowerVia hem Intel hem de IFS müşterileri için bir avantaj olmayı vaat ediyor. PowerVia BS PDN’nin somut bir fayda sağlayıp sağlamayacağını yalnızca zaman gösterecek, ancak TSMC’nin yalnızca benzer bir teknoloji sunması beklendiğinden, Intel’in arka taraf güç dağıtımlı yongalar yapmaya hazır ilk şirket olması dikkat çekicidir. 2026 sonu – 2027 başı.