Ölçeklendirmenin pek işe yaramadığı bir teknoloji ürünü varsa o da DRAM’dir. Bunun birçok nedeni vardır; en önemlisi DRAM hücrelerinin gerçek tasarımı ve bunun üretimle olan ilişkisidir. Ancak Lam Research’e göreBu ölçeklendirme zorluklarının nihai sonucu, DRAM alanındaki araştırmacıların bundan beş yıl sonra bile DRAM’in yoğunluk ölçeklendirmesini artırma yollarının dışında olabileceği anlamına geliyor.

Yarı iletken devre tasarımında uzmanlaşmış bir şirket olan Lam Research, bu bağlamda gelecekteki DRAM ürünlerinin nasıl gelişebileceğine dair bir teklif yayınladı. Ve bu gelecek pekala 3 boyutlu olabilir, dolayısıyla öyle görünüyor ki bellek küpleri olasılıklar alanının o kadar da dışında değil. Şirkete göre, üretilebilir bir 3D DRAM cihazı tasarlamak yaklaşık beş ila sekiz yılımızı alacak ve bu da dünyaya 2D DRAM ölçeklendirmesinin sona ermesi ile 3D DRAM ölçeklendirmesinin başlaması arasında üç yıllık olası bir boşluk bırakacak.

Kendi mülkiyetlerini kullanarak SEMulator3D Lam Research, olası 3D DRAM tasarımlarını yineledi. Odaklandıkları nokta ölçeklendirme ve katman istifleme zorluklarını, kapasitör ve transistör küçültmeyi, hücreler arası bağlantıyı ve diziler (TSMC’nin TSV’si gibi) aracılığıyla çözmekti. [Through Silicon Vias], bunu zaten diğer 3 boyutlu yarı iletken tasarımlarda da gördük). Son olarak şirket, önerilen tasarımın üretilmesini mümkün kılan süreç gereksinimlerini belirledi.

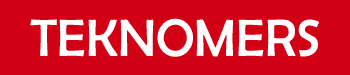

DRAM hücrelerinin tasarlanma şekli nedeniyle, 2D DRAM bileşenlerini basitçe yan yatırıp daha sonra üst üste istiflemek mümkün olmayacaktır. Bunun nedeni, DRAM hücrelerinin yüksek en-boy oranına sahip olmasıdır (kalın olduklarından daha uzun olmalarıdır). Bunları yan yatırmak, mevcut kapasitemizin ötesinde yanal gravür (ve doldurma) yetenekleri gerektirecektir.

Ancak mimarinin kendisini anladığınızda, tasarım kısıtlamalarının etrafından dolaşmaya çalışırken onu değiştirebilir ve uyarlayabilirsiniz. Ancak bunu söylemek yapmaktan daha kolaydır ve halihazırda 3D DRAM’e sahip olmamamızın bir nedeni var.

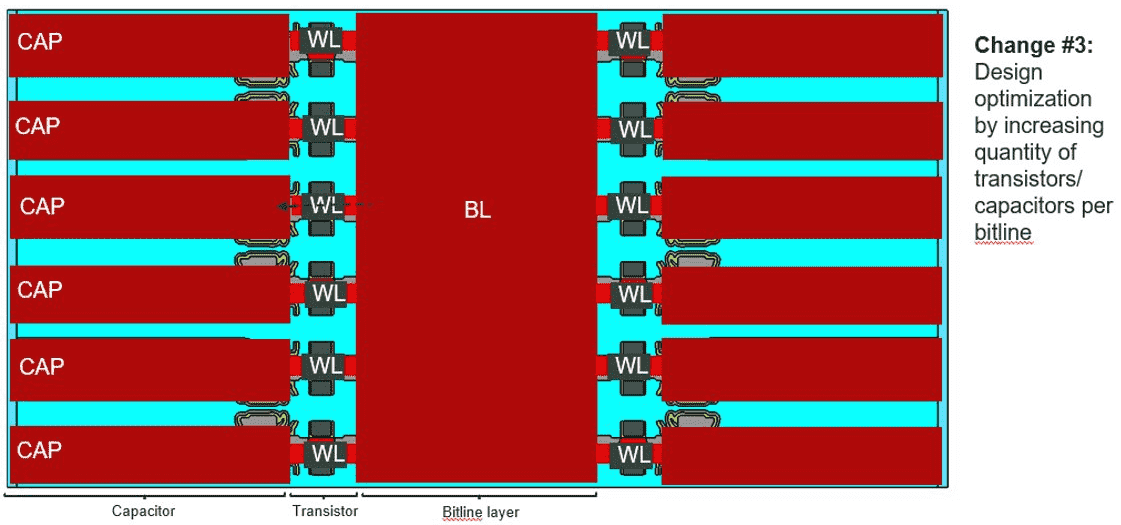

Mevcut DRAM devre tasarımları esasen üç bileşene ihtiyaç duyar: bir bit hattı (akımı enjekte eden iletken bir yapı); bit hattının akım çıkışını alan ve elektrik akımının devreye akıp akamayacağını (ve devreyi doldurup dolduramayacağını) kontrol eden geçit görevi gören bir transistör; ve bit hattından ve transistörden akan akımın sonuçta bir bit (0 veya 1) biçiminde depolandığı bir kapasitör.

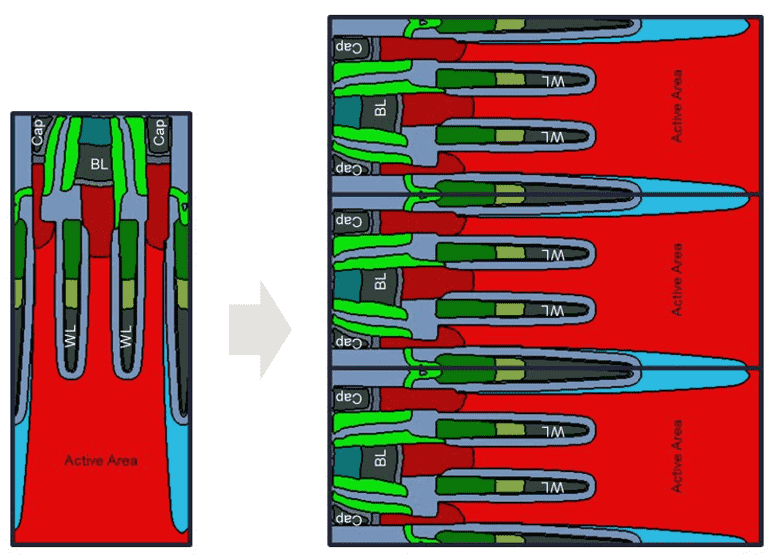

Lam Research, çalışan bir mimariye ulaşmak için birkaç çip tasarımı “püf noktası” kullandı. Birincisi, bit hattını transistörün karşı tarafına taşıdılar; bit hattı artık kapasitör tarafından çevrelenmediğinden, bu, bit hattının kendisine daha fazla transistörün bağlanabileceği anlamına gelir ve bu da çip yoğunluğunu artırır.

Alan yoğunluğu kazanımlarını en üst düzeye çıkarmak için Lam Research ayrıca birkaç son teknoloji transistör üretim tekniğini de uyguladı. Bunlar arasında Intel’in yeni nesil geçit teknolojileri için araştırdığı görünen Her Yerde Geçit (GAA) çatal sayfası tasarımları da yer alıyor. Lam araştırması tarafından önerilen yeniden tasarlanan DRAM mimarisi daha sonra NAND’ınkinden farklı olmayan bir süreçte yeni DRAM hücre tasarımının katmanları üst üste gelecek şekilde istiflenebilir.

Ancak NAND ölçeklendirmesi şu anda 232 katman civarında olsa da Lam Research, kendisininki gibi ilk nesil 3D DRAM tasarımının yalnızca 28 yığılmış katmandan yararlanabileceğini tahmin ediyor. Lam Research, mimari iyileştirmeler ve ek katmanlamayla DRAM yoğunluğunda iki düğümlü bir sıçrama iyileştirmesinin elde edilebileceğini tahmin ediyor; DRAM gökdelenine ek katmanlar ekleyerek daha fazla iyileştirmenin mümkün olabileceğini tahmin ediyor. Diğer üretim teknolojilerinde gördüğümüz gibi, daha sonra bireysel katmanları birbirine bağlamak için bir geçiş dizisinin (TSMC’nin TSV’sini destekleyen teknoloji) kullanımı kullanılır.

Ancak Lam Research’ün önerdiği tasarımla ilgili acil bir sorun var: İhtiyaç duyulan özellikleri güvenilir bir şekilde üretebilecek mevcut üretim araçları yok. Şirket, DRAM tasarımının günümüzün en ileri noktasında yaşadığını belirtmekte gecikmedi; Araç ve süreçlerin iyileştirilmesi ve yeniden tasarlanması ortak bir gerekliliktir. Şirketin ifadesine göre DRAM ölçeklendirme duvarına çarpmadan önce hala zamanımız var. Umuyoruz ki gerekli araçlar ve uzmanlık bu zaman dilimi içerisinde gelecektir.