Intel, bugün Meteor Lake, Arrow Lake ve Lunar Lake yongaları için kullanacağı 3D Foveros yonga tasarımı hakkında daha fazla yeni ayrıntıyı, şirketin teknoloji paylaşımının devlerini gören bir yarı iletken endüstri konferansı olan Hot Chips 34’teki sunumunun bir teaser’ı olarak açıkladı. yeni işlemcilerinin mimari detayları. Intel CEO’su Pat Gelsinger etkinliğin açılış konuşmasını yapacak ve şirketin ayrıca burada tartışacağımız tüketici ‘Lake’ işlemcileri ve Ponte Vecchio GPU’ları, FPGA’ları ve Xeon D işlemcileri de dahil olmak üzere dört teknik sunumu var.

Her şeyden önce, Intel’in GPU döşemesi/yongası için TSMC 3nm düğümünden 5nm düğümüne geçmesi nedeniyle Intel’in Meteor Gölü’nün piyasaya geç çıkacağına dair son söylentiler var. Intel, GPU için hangi düğümü kullanacağı konusunda hala bilgi paylaşmıyor olsa da, şirket temsilcileri GPU kutucuğu için planlanan düğümün değişmediğini ve işlemcinin 2023’te zamanında piyasaya sürülme yolunda olduğunu söylüyor.

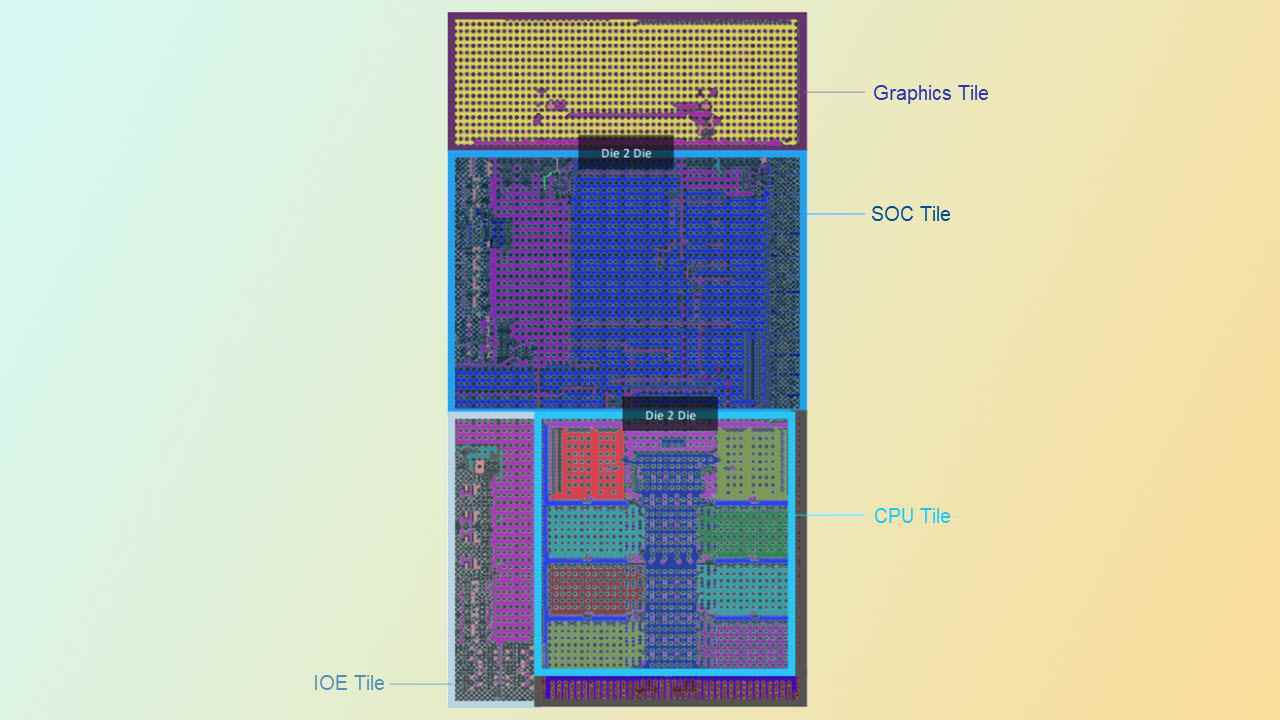

Yukarıdaki albümdeki ilk görüntü, Intel’in Meteor Lake işlemcilerinin paylaştığı yeni bir diyagramdır. Intel 4 işlem düğümü kapsamımızdan aşağıdaki slaytları da ekledik. Yeni görüntüde birkaç yeni ayrıntı var — Intel, bu diyagramın pazara altı performans çekirdeği ve iki küme verimlilik çekirdeği ile gönderilecek bir mobil işlemci olduğunu söylüyor. Intel doğrulamadı, ancak bunların sırasıyla Redwood Cove ve Crestmont mimarilerine sahip olduğu düşünülüyor. Meteor Lake ve Arrow Lake yongaları, mobil ve masaüstü bilgisayar pazarının ihtiyaçlarını karşılayacak şekilde ölçeklenirken, Lunar Lake mobil 15W ve altı pazara hizmet edecek.

Paketleme ve ara bağlantı gelişmeleri, modern işlemcilerin çehresini hızla değiştiriyor. Her ikisi de artık temeldeki süreç düğümü teknolojisi kadar önemli – ve bazı yönlerden tartışmasız daha önemli –.

Intel’in bugün yaptığı açıklamaların çoğu, tüketici pazarı için Meteor Lake, Arrow Lake ve Lunar Lake işlemcileri için bir temel olarak kullanacağı 3D Foveros paketleme teknolojisine odaklanıyor. Bu teknoloji, Intel’in bir Foveros ara bağlantısı ile tek bir birleştirici temel kalıbın üzerine yongaları dikey olarak istiflemesine olanak tanır. Intel ayrıca Ponte Vecchio ve Rialto Bridge GPU’ları ve Agilex FPGA’ları için Foveros kullanıyor, bu nedenle bu, şirketin yeni nesil ürünlerinin birçoğu için temel bir teknolojidir.

Intel, ilk olarak düşük hacimli Lakefield işlemcilerinde 3D Foveros’u piyasaya sürdü, ancak dört karolu Meteor Lake ve yaklaşık 50 karolu Ponte Vecchio, şirketin teknolojiye sahip ilk yüksek hacimli yonga üretimidir. Arrow Lake’den sonra Intel, yeni UCIe ara bağlantısına geçecek ve böylece standartlaştırılmış bir arayüz kullanan chipletlerin oluşturma ekosisteminden faydalanacak.

Intel, dört Meteor Lake yongasını (Intel dilinde ‘karolar’ olarak adlandırılır) TSV bağlantıları aracılığıyla pasif bir Foveros aracı/temel kutucuğuna yerleştireceğini açıkladı, yani aracının herhangi bir mantığı yok. Buradaki temel karo, bir tür SoC işlevi gören Lakefield’de bulunandan farklıdır. 3D Foveros teknolojisi ayrıca aktif aracıları da destekler. Intel, Foveros aracısını düşük maliyetli ve düşük güçte optimize edilmiş 22FFL işlemiyle (Lakefield ile aynı) ürettiğini söylüyor. Intel ayrıca dökümhane hizmetleri için bu düğümün daha yeni bir ‘Intel 16’ varyantına sahiptir, ancak Intel’in Foveros destekli yongaları için hangi sürümü kullanacağı açık değildir.

Intel, Intel 4 sürecini (burada daha fazlası), G/Ç döşemesini, SoC döşemesini ve grafik döşemesini (tGPU) kullanan hesaplama döşemesini bu aracının üzerine monte edecektir. Bu birimlerin tümü Intel tarafından tasarlanmıştır ve Intel mimarilerine sahiptir, ancak harici dökümhane TSMC, G/Ç, SoC ve GPU döşemelerini üretecektir. Bu, Intel’in yalnızca CPU ve Foveros döşemelerini üreteceği anlamına gelir. (Özellikle Intel, G/Ç kutucuğuna ‘G/Ç Genişletici’ adını verir, dolayısıyla IOE takma adıdır.)

Foveros, 36 mikronluk bir çarpma aralığı kullanır (ara bağlantı yoğunluğunun kritik bir ölçümü), ancak Intel’in gelecekteki tasarımlarla birlikte 25 ve 18 mikron aralıkları içeren bir yol haritası vardır. Gelecekte Intel, 1 mikronluk çarpma aralıklarına ulaşmak için teorik olarak hibrit bağlama ara bağlantılarını (HBI) bile kullanabileceğini söylüyor.

Egzotik 3D paketlemeyle ilgili en önemli endişelerden biri maliyet olmuştur ve Foveros, Intel’in öncü paketleme teknolojisiyle yüksek hacimli üretime ilk adımı olacaktır. Ancak Intel, 3D Foveros ambalajıyla üretilen yongaların, standart monolitik (tek kalıplı) yonga tasarımlarıyla fiyat açısından son derece rekabetçi ve belki de daha ucuz olacağını söylüyor.

Intel, Foveros kalıbını mümkün olduğunca düşük maliyetli olacak şekilde tasarladı – Meteor Lake paketindeki büyüklük sıralarına göre en ucuz kalıp – şirketin elektrik ve performans hedeflerini yerine getirirken. Intel, Foveros ara bağlantı/temel kutucuğu için henüz hızları ve beslemeleri paylaşmıyor, ancak arayüzlerin pasif konfigürasyonda ‘çoklu GHz’de’ çalışabileceğini söylüyor (bu ifade, Intel’in aracının aktif sürümlerinin halihazırda geliştirilmekte olduğunu da büyük ölçüde ima ediyor) . Bu nedenle, Foveros, tasarım ödünleşimleri gerektiren herhangi bir bant genişliği veya gecikme kısıtlamasına maruz kalmaz. Intel ayrıca tasarımın hem performans hem de maliyet açısından iyi bir şekilde ölçeklenmesini beklemektedir, yani diğer segmentler için ya değeri optimize edilmiş tasarımlar ya da performansa yönelik varyantlar yapabilir.

Ancak, büyük resme uzaklaştığımızda gerçek tasarrufları görüyoruz. Endüstri, verim endişeleri nedeniyle özellikle monolitik tasarımlarda daha küçük düğümlere doğru ilerledikçe, öncü düğümler transistör başına katlanarak daha pahalı hale geliyor. Ek olarak, daha küçük düğümler için G/Ç arayüzleri gibi yeni IP blokları tasarlamak, yatırım için çok fazla getiri sağlamaz. Bu nedenle, ‘yeterince iyi’ eski düğümlerde kritik olmayan döşemelerin/yongaların yeniden kullanılması, test sürecini basitleştirmenin yanı sıra zamandan, maliyetten ve geliştirme kaynaklarından tasarruf sağlar.

Monolitik bir kalıp için Intel’in bellek veya PCIe arabirimleri gibi farklı yonga öğelerini seri olarak test etmesi gerekir. Buna karşılık Intel, zaman kazanmak için chiplet’leri aynı anda test edebilir. Foveros ayrıca, farklı yongalar tasarımın ihtiyaçlarına göre uyarlanabildiğinden, belirli TDP aralıkları için yonga tasarlamada avantajlar sağlar.

Bu noktaların çoğunun çok tanıdık geldiğini düşünüyorsanız, haklısınız – bunlar AMD’yi 2017’de yonga yolundan aşağı iten faktörlerin aynısı ve büyük etki. AMD, yonga tabanlı bir tasarım kullanan ilk kişi değildi, ancak tasarım felsefesini kullanarak seri üretim modern bir yonga tasarlayan ilk kişiydi, bu nedenle Intel teknolojiye biraz geç kaldı. Bununla birlikte, Intel’in 3D paketleme teknolojisine olan ilk baskısı, AMD’nin hem avantajları hem de dezavantajları olacak organik aracı tabanlı tasarımlarından çok daha karmaşıktır. Kanıt, Intel’in 2023 lansmanı için yolda olduğunu söylediği son silikonda olacak.

İşte Intel’in bu hafta Hot Chips 34’te ele alacağı konulara genel bakış. Gerçek sunumlar gerçekleştikçe daha derinlemesine bilgi sahibi olacağız, bu nedenle bu makalenin yakında bir güncellemesini bekleyebilirsiniz. Bizi izlemeye devam edin.