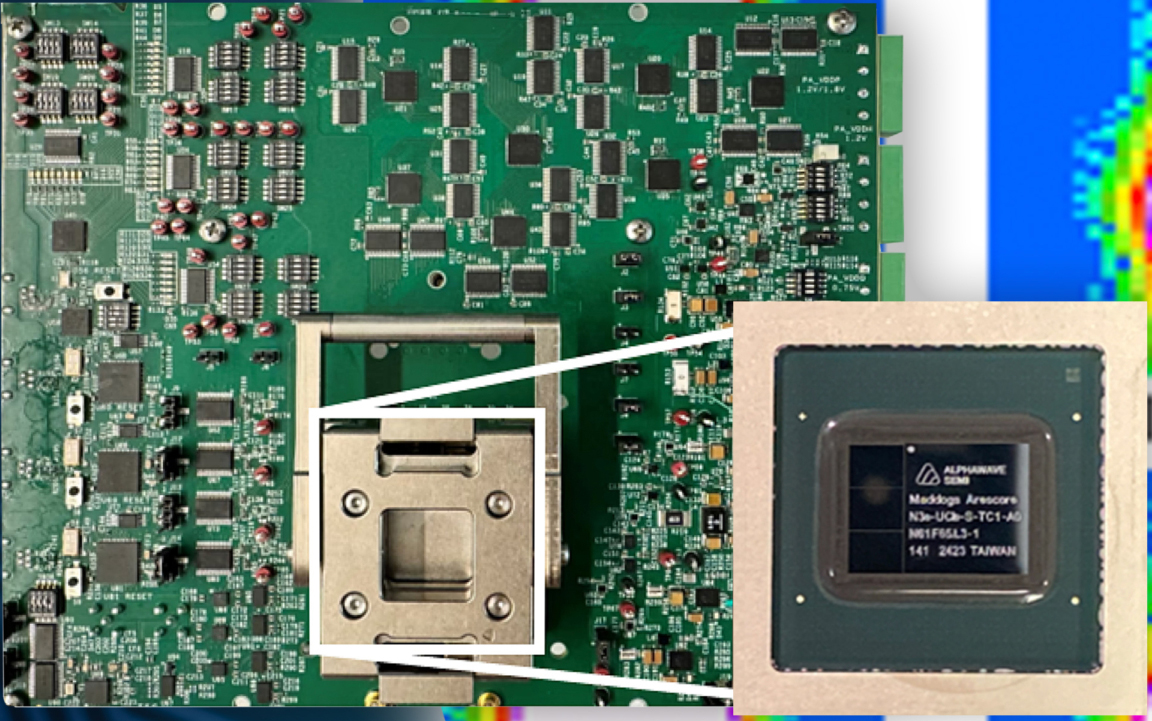

IP ve sözleşmeli çip tasarımcısı olan Alphawave Semi, gelişmiş TSMC’nin yonga-üzeri-alt tabaka (CoWoS) paketleme teknolojisinde üretilen sistem-paketleri için kalıptan kalıba bağlantı sağlayan sektörün ilk 3nm UCIe yongası. Yonga, hiper ölçekleyiciler, HPC ve AI gibi yüksek talep gören sektörleri hedefliyor ve kullanıcıların çok çeşitli sistem-paketleri (SiP’ler) oluşturmasına olanak sağlıyor.

Alphawave Semi’nin Özel Silikon ve IP Kıdemli Başkan Yardımcısı ve Genel Müdürü Mohit Gupta, “TSMC’nin gelişmiş paketlemesiyle 3nm 24 Gbps UCIe alt sisteminin başarılı bir şekilde silikon haline getirilmesi, Alphawave Semi için önemli bir dönüm noktasıdır ve şirketin en üst düzey bağlantı çözümleri sunmak için TSMC 3DFabric ekosistemini kullanma konusundaki uzmanlığını vurgulamaktadır” dedi.

3nm yongacık, UCIe 1.1 uyumlu yongacıkları bağlamak için ayrı ayrı kullanılabilmesine rağmen, IP’nin temel amacı, Alphawave Semi (müşterileri için) veya IP’yi lisanslayan şirketler tarafından kalıptan kalıba bağlantı sağlamak için diğer yongacıklara entegre edilmesidir. Silikonla kanıtlanmış 3nm kalıptan kalıba arayüz IP’si, TSMC’nin bugüne kadarki en gelişmiş üretim süreci kullanılarak uygulanan çoklu yongacık SiP’lerinin oluşturulmasına olanak tanıdığı için pazar için büyük bir öneme sahiptir.

TSMC’nin N3 üretim düğümlerinin kullanımı pahalı olduğundan, büyük monolitik tasarımların parçalanması verimi artırmanın iyi bir yoludur ve Alphawave’in silikonla kanıtlanmış 3nm kalıptan kalıba arayüz IP’sinin devreye girdiği yer burasıdır. TMSC’nin CoWoS’uyla uyumluluk IP için önemli bir yetenektir.

3nm yongacık, 8 Tbps/mm bant genişliği yoğunluğunu destekler ve TSMC’nin CoWoS 2.5D silikon ara parça tabanlı paketlemesini hedefler; bu, Nvidia’nın Hopper H100 ve AI ve HPC uygulamaları için yeni nesil Blackwell B100 ve B200 GPU’ları için kullandığı paketlemeyle aynıdır. Alphawave Semi’nin UCIe yongacık alt sistemi hem PHY hem de denetleyici IP’sini paketler ve akış, PCIe, CXL, AXI-4, AXI-S, CXS ve CHI dahil olmak üzere çok çeşitli protokolleri destekler. Yongacık, bir SiP’de çeşitli 3nm bileşenleri bağlayabilir.

Alphawave Semi’nin UCIe alt sistem IP’si en son UCIe Spesifikasyonu Rev 1.1’e uygundur ve JTAG, BIST, DFT ve Bilinen İyi Kalıp (KGD) işlevleri dahil olmak üzere kapsamlı test ve hata ayıklama özellikleriyle donatılmıştır. Bu IP’nin bir diğer öne çıkan özelliği, şerit sağlığını gerçek zamanlı olarak izleme yeteneğidir — bu da SiP’nin sağlamlığını büyük ölçüde artırır.