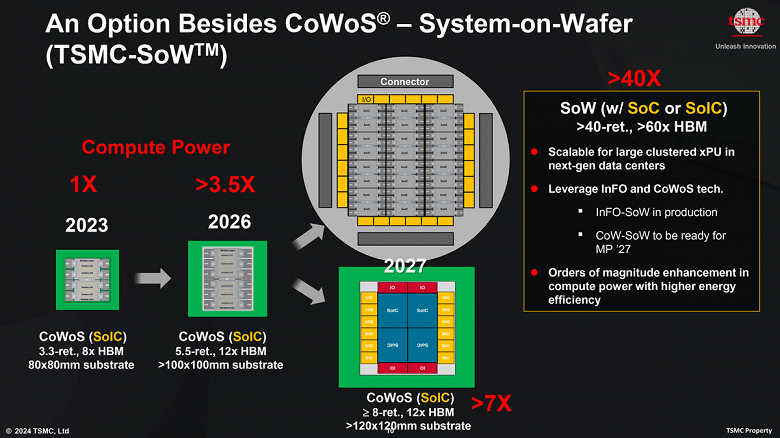

Sadece birkaç yıl içinde TSMC, mevcut rekor sahiplerinin iki katından daha büyük dev çipler üretebilecek.

CoWoS paketleme teknolojisinin yeni versiyonu, TSMC’nin iki ila üç yıl içinde 120 x 120 mm boyutlarında paketlere sahip çipler üretmesine olanak tanıyacak!

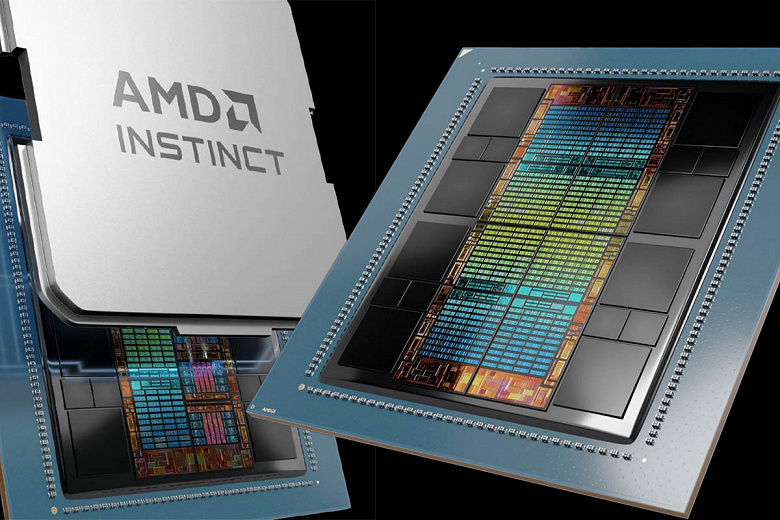

Mevcut CoWoS teknolojisi, TSMC’nin fotomaskın yaklaşık 3,3 katı boyutunda silikon ekler oluşturmasına olanak tanıyor. Böylece CPU veya GPU’nun kendisi, sekiz HBM3/HBM3E bellek yığını, G/Ç yongaları ve diğerleri, maksimum 80×80 mm alt tabaka boyutuyla toplam 2831 mm2’ye kadar çıkabilir.

2026’da üretime hazır olacak yeni nesil CoWoS_L, ağın yaklaşık 5,5 katı büyüklüğünde aracıları kullanabilecek. Yani bir dizi çip için 4719 mm²’lik bir alan mevcut olacaktır. Bu tür SiP’ler ayrıca daha büyük levhalar gerektirecektir ve TSMC slaytına bakılırsa 100×100 mm’den bahsediyoruz.

Zaten 2027’de TSMC, 120×120 mm alt tabakaya ve 6864 mm kullanılabilir alana sahip çipler oluşturabilecek2. Çok daha küçük boyutlara sahip modern çiplerin ne kadar tükettiği göz önüne alındığında, bu tür canavarların birkaç kilowatt enerjiye ihtiyaç duyacağını varsayabiliriz.

Elbette, kare şeklinde kesildikten sonra aslında 300 mm’lik silikon levhanın tamamını kaplayan Cerebras çiplerinin boyutu ve tüketimi, belirtilen TSMC çözümlerinden uzaktır, ancak Cerebras benzersiz bir özel çözümü ve CoWoS’un yeni versiyonunu temsil etmektedir. çeşitli görevler için canavar çipleri oluşturmanıza olanak tanır.