Intel ve TSMC, dikey olarak istiflenmiş tamamlayıcı alan etkili transistörler (CFET’ler) konusundaki ilerlemelerini yaklaşan Uluslararası Elektron Cihazları Toplantısı (IEDM) konferansında açıklayacak, raporlara göre eeHaberlerAvrupa. CFET’ler, muhtemelen önümüzdeki on yıl içinde, her yönüyle geçit (GAA) transistörlerinin (henüz pazarı kendileri devralmak zorunda) yerini alacak şekilde ayarlandı.

N ve p tipi transistörlerin üst üste yerleştirilmesini içeren CFET kavramı, ilk olarak 2018 yılında IMEC araştırma enstitüsü tarafından tanıtıldı. İlk çalışmaların çoğu akademik çevrelerden kaynaklansa da, Intel ve TSMC gibi ticari şirketler artık bu konuya girişti. arenadayız ve bu yeni nesil transistör tipini aktif olarak araştırıyoruz.

Intel

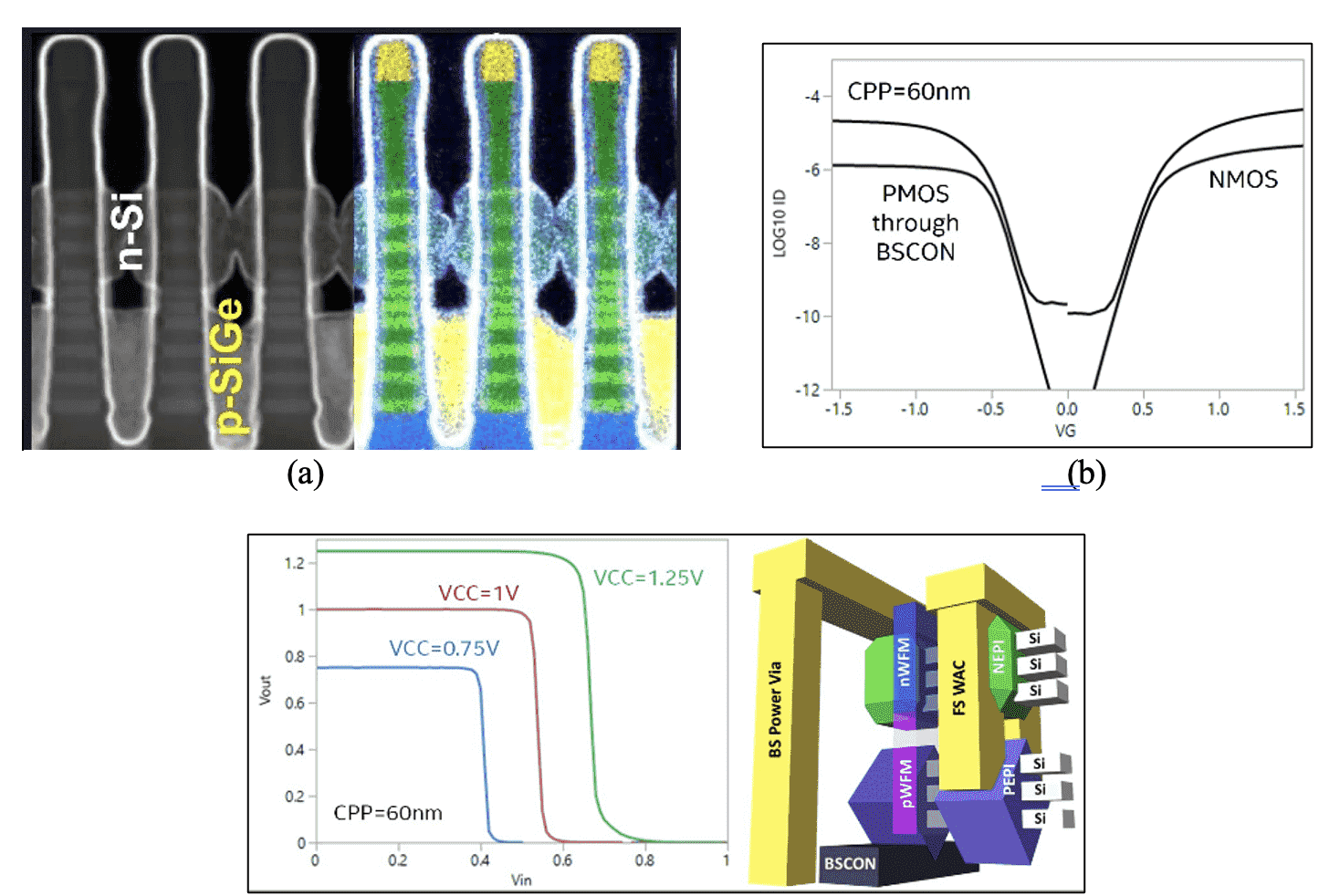

Intel’in araştırmacıları, 30nm’lik dikey boşluğu koruyan, üç p-FET nanoşeridin üzerinde katmanlanan üç n-FET nanoşeridi içeren monolitik bir 3D CFET inşa etti. Intel’in ” başlıklı sunumu60nm Kapı Aralığında, Güç Yoluyla ve Doğrudan Arka Taraf Cihaz Kontaklarıyla Yığılmış CMOS İnvertörün Gösterimi“, 60nm kapı aralığında CFET kullanan işlevsel invertör test devrelerini açıklayacaktır. Bu tasarım aynı zamanda dikey katmanlı çift kaynak-drenajlı epitaksi ve ikiz metal kapı yığınlarının yanı sıra şirketin PowerVia arka taraf güç dağıtımını da içerir.

TSMC

Rakibini geride bırakmamak için TSMC, mantık teknolojisi için özel olarak tasarlanmış ve 48nm kapı aralığına sahip uygulamalı CFET yöntemini tartışacak. Dökümhanenin tasarımı, p-tipi muadillerinin üzerine yerleştirilmiş katmanlı n-tipi nano tabaka transistörleri vurguluyor ve altı büyüklük mertebesini kapsayan dikkate değer bir açma/kapama akım oranına sahip.

Şirkete göre TSMC’nin transistörleri %90’ın üzerinde başarılı testlerle dayanıklılıklarını kanıtladı. Şirket, CFET teknolojisinin yeteneklerinden tam anlamıyla yararlanmak için özümsenmesi gereken daha fazla özellik olduğunu kabul etse de, devam eden çalışma bu hedefe yönelik çok önemli bir adımı temsil ediyor.

Yeni Nesil Transistör

CFET’ler, iki transistörün bir transistörün kapladığı alana sığmasına izin veren dikey istiflemeleriyle transistör tasarımında dikkate değer bir değişiklik getiriyor ve böylece bir çip üzerindeki transistör yoğunluğunu artırıyor. Bu tasarım yalnızca gelişmiş alan verimliliğinin önünü açmakla kalmıyor, aynı zamanda daha akıcı bir CMOS mantık devre düzenini de destekleyerek tasarım verimliliğinin artmasını kolaylaştırıyor.

Ek olarak, CFET’lerin doğal yapısı parazitik etkilerin azalmasına yol açarak performans ve güç verimliliğinde potansiyel iyileştirmeler sunabilir. NMOS ve PMOS kanal varyasyonlarını dengeleme yeteneği gibi uyarlanabilir tasarım yetenekleri, arka taraftan güç dağıtımı gibi yeniliklerle birleştiğinde üretim sürecini daha da kolaylaştırarak CFET’leri transistör teknolojisi alanında umut verici bir gelişme haline getiriyor.

Hem Intel’in hem de TSMC’nin çabaları, CFET teknolojisinin yarı iletken endüstrisinin geleceği açısından önemini vurguluyor.