TSMC ifşa N3 (3 nanometre sınıfı) proses teknolojileri ailesi için bu hafta 2023 Kuzey Amerika Teknoloji Sempozyumunda önemli yol haritası güncellemeleri. TSMC’nin FinFET transistörlerine dayalı son yüksek performanslı düğümü olan N3, uzun yıllar dayanacak ve N3E’nin performansı artıran bir optik küçültme olan N3P ve yüksek sızıntı ve gücü tolere eden HPC uygulamaları için performans odaklı N3X dahil olmak üzere birden fazla sürüm içerecektir. .

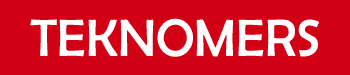

TSMC’nin N3 (N3B olarak da bilinir) proses teknolojisi üzerindeki seri üretimi halihazırda devam etmektedir, ancak bu düğüm, 25 katmana kadar aşırı ultraviyole litografi kullanır ve hatta EUV çift modellemeyi kullanabilir, bu da onu kullanımı özellikle pahalı bir düğüm haline getirir. Sonuç olarak TSMC, müşterilerinin çoğunluğunun EUV’yi 19 katmana kadar kullanabilen, çift modelleme EUV kullanmayan, daha geniş bir işlem penceresine ve daha iyi verime sahip N3E’yi kullanmasını beklemektedir. 2023’ün ikinci yarısında yüksek hacimli üretim için kullanılacak olan N3E, TSMC’nin 3nm’lik sonraki evriminin de temelini oluşturacak.

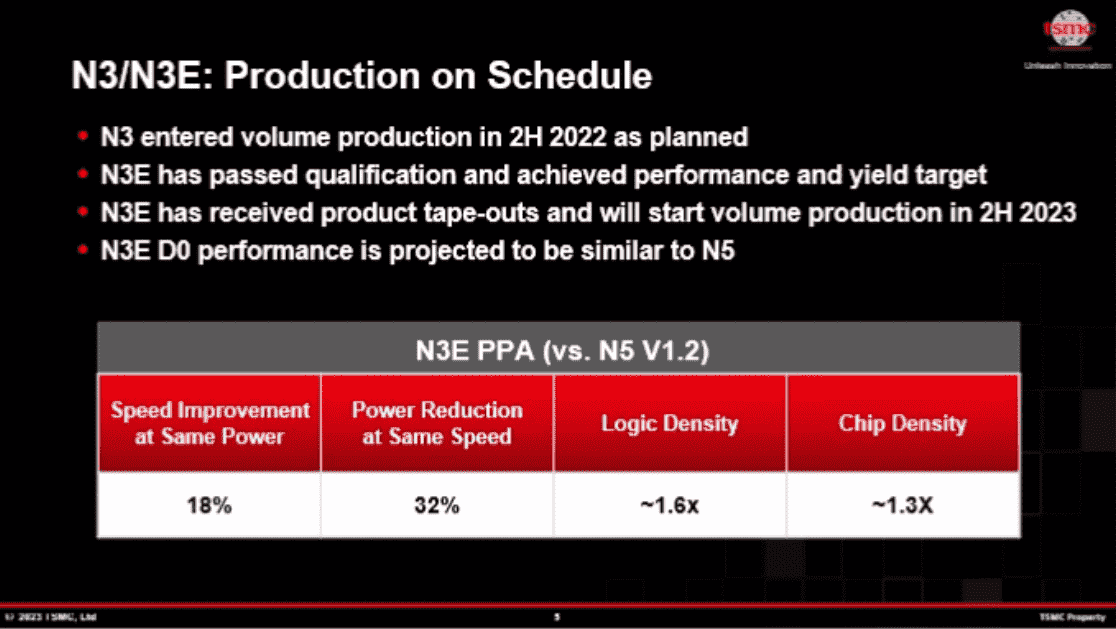

Bu evrimdeki ilk adım N3P olacak. Bu teknoloji büyük ölçüde, aynı sızıntıda %5 performans artışı, aynı saatlerde %5 ila %10 güç azaltma ve %4 daha yüksek transistör yoğunluğu sağlayan diğer bazı iyileştirmeleri içerecek olan N3E’nin optik küçültülmesi olacaktır. %50 mantık, %30 SRAM ve %20 analog devrelerden oluşan karma çip.

N3E’nin optik küçültücüsü olan N3P, tasarım kurallarını koruyarak çip tasarımcılarının N3E IP’yi yeni düğümde yeniden kullanmalarına izin verir. Ansys, Cadence ve Synopsys gibi IP tasarım şirketlerinin zaten N3E çiplerini hedefleyen çok sayıda IP’si olduğundan, bu oldukça önemlidir. Bu arada, optik büzülme, son yıllarda büzülme mücadelesi veren bir devre türü olan SRAM dahil olmak üzere her türlü transistör ve devre için yoğunluk iyileştirmeleri anlamına gelir (bu, özellikle modern SRAM yoğun tasarımlar için kötü bir şeydir). N3P, 2024’te seri üretime hazır olacak.

N3P’nin ardından TSMC, N3 ailesini daha da genişletmeyi ve N3X ile CPU’lar ve GPU’lar gibi yüksek performanslı bilgi işlem uygulamalarına dallandırmayı planlıyor. Bu üretim sürecinin, N3P’ye kıyasla en az %5 daha yüksek frekanslar sağlaması ve aynı zamanda önemli ölçüde daha yüksek voltajlara izin vermesi öngörülüyor, bu da daha yüksek genel sızıntı pahasına saatleri daha da artıracak.

| Satır 0 – Hücre 0 | N3X ve N3P | N3P ve N3E | N3E’ye karşı N5 | N3 ve N5 |

| Aynı Güçte Hız İyileştirme | +5% Fmaks @ 1,2V | +%5 | +%18 | +%10 ~ %15 |

| Aynı Hızda Güç Azaltma | ? | -5% ~ -10% | -32% | -25% ~ -30% |

| Mantık Yoğunluğu | Aynı | 1,04x | 1,7x | 1,6x |

| HVM Başlatma | 2025 | H2 2024 | Q2/Q3 2023 | H2 2022 |

TSMC, N3X düğümünün, 3 nm sınıfı bir üretim teknolojisi için oldukça yüksek bir voltaj olan en az 1,2 V’u işleyebileceğini iddia ediyor. TSMC, N3P’ye kıyasla güç sızıntısında %250’lik şaşırtıcı bir artış beklediğinden, bu önemli bir değiş tokuşla birlikte gelir. Bu, N3X’in öncelikle HPC CPU’lar için uygun olduğunu ve çip tasarımcılarının veri merkezi CPU’ları ve bilgi işlem GPU’ları gibi en yüksek performansa sahip güce aç çipleri geliştirirken dikkatli olmalarını gerektireceğini vurgulamaktadır.

Transistör yoğunluğu açısından N3X, N3P’nin yetenekleriyle eşleşecektir. TSMC, N3P ve N3E’nin uyumlu tasarım kurallarına sahip olup olmayacağını belirtmedi ve tasarımların iki düğüm arasında taşınıp taşınamayacağı konusunda entrikalara yer bıraktı.