Rambus sadece ilan edildi yeni nesil veri merkezine ve yapay zeka çözümlerine gelen yepyeni PCIe 6.0 arabirim alt sistemi.

Rambus, Yüksek Performanslı Veri Merkezleri ve Yapay Zeka SoC’leri için PCIe 6.0 Arayüz Alt Sistemini Sağlıyor

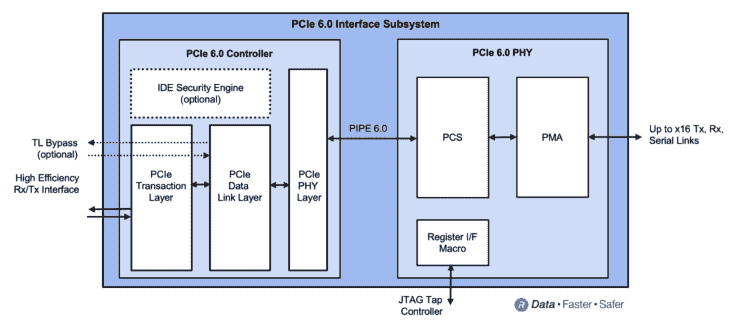

Basın bülteni: Verileri daha hızlı ve daha güvenli hale getiren önde gelen bir çip ve silikon IP sağlayıcısı olan Rambus Inc. (NASDAQ: RMBS), bugün PHY ve kontrolör IP’sinden oluşan PCI Express® (PCIe®) 6.0 Arayüz Alt Sisteminin kullanıma sunulduğunu duyurdu. Rambus PCIe Express 6.0 PHY ayrıca Compute Express Link (CXL) spesifikasyonunun en son sürümü olan sürüm 3.0’ı da destekler.

Rambus Arayüz IP genel müdürü Scott Houghton, “AI/ML’nin hızlı gelişimi ve veri yoğun iş yükleri, daha yüksek performans seviyeleri gerektiren veri merkezi mimarilerinin sürekli evrimini yönlendiriyor” dedi. “Rambus PCIe 6.0 Arabirim Alt Sistemi, sınıfının en iyisi gecikme, güç, alan ve güvenlik ile yeni nesil veri merkezlerinin performans gereksinimlerini destekler.”

Rambus PCIe 6.0 Arayüz Alt Sistemi, saniyede 64 Gigatransfer’e (GT/s) kadar veri hızları sunar ve gelişmiş heterojen bilgi işlem mimarilerinin ihtiyaçlarını karşılamak için tamamen optimize edilmiştir. Alt sistem içinde, PCIe denetleyicisi, PCIe bağlantılarını ve bunlar üzerinden aktarılan değerli verileri korumaya adanmış bir Bütünlük ve Veri Şifreleme (IDE) motoruna sahiptir. PHY tarafında, önbellekle uyumlu bellek paylaşımı, genişletme ve havuzlama için çip düzeyinde çözümleri etkinleştirmek için CXL 3.0 için tam destek mevcuttur.

PCI Express katmanı

- En yeni PCI Express 6.0 (64 GT/s), 5.0 (32 GT/s), 4.0 (16 GT/s), 3.1/3.0 (8 GT/s) ve PIPE 6.x (8, 16, 32, 64 ve 128 bit) özellikler

- SerDes Mimarisini destekler BORU 10b/20b/40b/80b genişliği

- Orijinal BORU braketleri 8b/16b/32b/64b/128b genişlik

- PCI-SIG Tek Köklü G/Ç Sanallaştırma (SR-IOV) Spesifikasyonu ile uyumlu

- FLIT ve FLIT olmayan modlarda birden çok sanal kanalı (VC’ler) destekler

- Uç Nokta, Kök Bağlantı Noktası, Çift mod, Anahtar bağlantı noktası yapılandırmalarını destekler

- PCIe 6.0 ila PCIe 1.0 hızlarını destekler

- İleri Hata Düzeltmeyi (FEC) destekler – Düşük gecikme için hafif algoritma

- L0p Düşük Güç modunu destekler

- Veri yolu için 4 bit’e kadar eşlik koruması

- Clock Gating ve Power Gating’i destekler

- RAS özellikleri arasında LTSSM zamanlayıcıları geçersiz kılma, ACK/NAK/Replay/UpdateFC zamanlayıcıları geçersiz kılma, şifrelenmemiş PIPE arabirim erişimi, Rx ve Tx yollarına hata enjeksiyonu, ayrıntılı kurtarma durumu ve çok daha fazlasını içerir ve görev açısından kritik IP’nin güvenli ve güvenilir bir şekilde dağıtılmasına olanak tanır SoC’ler

Bilgi İşlem Yarı İletkenleri bir IDC araştırma başkan yardımcısı Shane Rau, “PCIe, veri merkezinde her yerde bulunur ve şirketler yeni nesil uygulamalarda daha yüksek performans seviyelerini desteklemek için sürekli artan hızlar ve bant genişlikleri izledikçe CXL giderek daha önemli hale gelecektir” dedi. “Yeni veri merkezi mimarilerini desteklemek için artan sayıda çip şirketi ortaya çıktıkça, ekosistemi etkinleştirmenin anahtarı yüksek performanslı arayüz IP çözümlerine erişim olacaktır.”

Rambus PCIe 6.0 Arayüz Alt Sisteminin temel özellikleri şunları içerir:

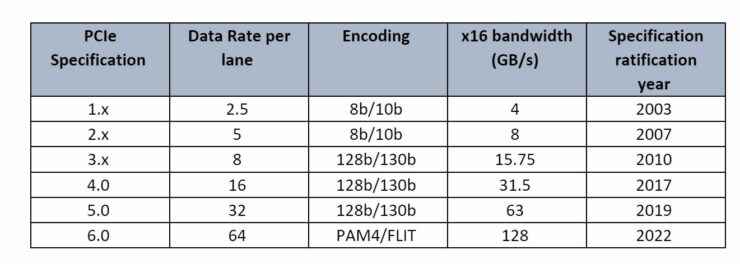

- 64 GT/s veri hızı ve PAM4 sinyali dahil PCIe 6.0 spesifikasyonunu destekler

- Bağlantı sağlamlığı için düşük gecikmeli İleri Hata Düzeltme (FEC) uygular

- Yüksek bant genişliği verimliliği sağlayan sabit boyutlu FLIT’leri destekler

- PCIe 5.0, 4.0 ve 3.0/3.1 ile geriye dönük uyumlu